#### DEPARTAMENTO DE ELECTRONICA

# Sistemas Digitales con Microprocesadores 112135

- 1. Arquitectura básica del microprocesador 8086

- 1.1 Arquitectura Interna BIU y EU

- 2. Especificaciones de hardware

- 3. Memoria

- 3.1 Lineal

- 3.2 Segmentada

- 4. Registros

- 5. Modos de Direccionamiento

- 6. Conjunto de instrucciones

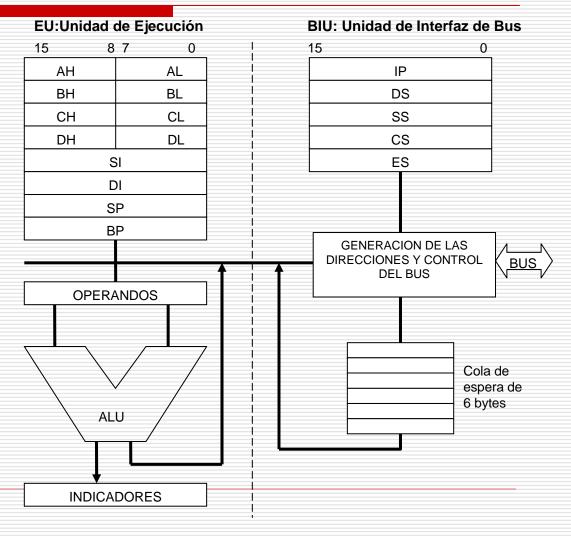

### 8086 Arquitectura Interna

El microprocesador

8086 se

encuentra

organizado como

dos procesadores

separados, la

unidad de interfaz

de bus (BIU) y la

unidad de

ejecución (EU).

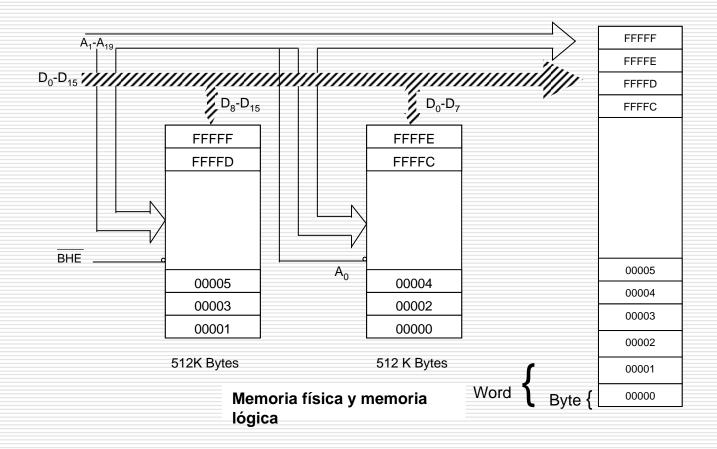

Memoria Lineal

#### Memoria Lineal

- MEMORIA: El espacio de direcciones de un sistema basado en un microprocesador, se referencia como memoria física o memoria lógica. En la mayoría de los casos la estructura de la memoria lógica es diferente de la estructura de memoria física. La memoria lógica es el sistema de memoria como lo ve el programador, mientras que la memoria física es la estructura de hardware actual del sistema de memoria.

- □ La memoria lógica del 8086 empieza en la localidad de memoria 00000H y se extiende hasta la localidad FFFFH. Este rango de direcciones especifica el mega byte de memoria disponible.

- Memoria Física: Cuando el microprocesador direcciona una palabra de 16 bits de memoria se acceden dos bytes consecutivos. Por ejemplo la palabra de la localidad 00122H se encuentra almacenada en el byte 00122H y 00123H con el byte menos significativo almacenado en la dirección 00122H. Si una doble palabra de 32 bits se almacena en la localidad 00120H esto implica que se almacena en los bytes 00120H, 00121H, 00122H y 00123H con el byte menos significativo almacenado en el byte 00120H y el byte mas significativo en la localidad 00123H.

- La memoria física en el 8086 es de 16 bits de ancho. Se encuentra compuesta por dos bancos de memoria cada uno de 512K bytes. La señal BHE' activa el banco alto (de direcciones nones) y la señal Ao activa el banco bajo (de direcciones pares).

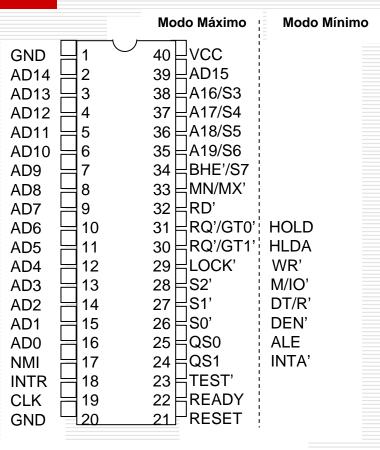

Especificaciones de hardware

El 8086 es un microprocesador de 16 bits con una capacidad de direccionamiento de memoria de 1 MB (220) y un espacio separado de puertos de E/S con una capacidad de 64 KB (2<sup>16</sup>). El CPU se comunica con su ambiente externo a través del bus multiplexado de direcciones, datos y status y un bus de control. Para transferir datos o buscar instrucciones, el CPU ejecuta un ciclo de bus.

Configuración de terminales del 8086

#### 8086 Arquitectura Interna

- La BIU proporciona las funciones de hardware, incluyendo la generación de direcciones de memoria y E/S para la transferencia de datos entre el procesador y el mundo exterior. Lee las instrucciones de la memoria y las almacena en una FIFO (cola de instrucciones) de 6 bytes, hasta que la EU las capte para ejecutarlas. Así la BIU se encarga de transferir los datos entre la memoria (o los puertos) y la CPU, y mientras tanto la EU está procesando una instrucción. La BIU siempre mantiene llena la cola de espera.

- □ La EU recibe los códigos de instrucción y datos de la BIU, ejecuta esas instrucciones, y almacena los resultados en los registros generales. A través de regresar los datos a la BIU, los datos pueden almacenarse en una localidad de memoria o escritos a un dispositivo de salida. La EU no tiene conexión directa con el sistema de buses. Recibe y transmite todos sus datos a través de la BIU.

- **Registros de Datos**. Incluye el acumulador AX y registros BX, CX y DX. Cada registro es de 16 bits pero pueden accederse como registros tamaño byte o palabra. Esto es, BX es el registro base de 16 bits mientras que BH hace referencia al byte de mayor orden del registro base. Los registros de datos normalmente se utilizan para almacenar resultados temporales de instrucciones .

- AX.- Registro acumulador, dividido en AH y AL (8 bits cada uno). Al usarlo se genera una instrucción que ocupa un byte menos que si se utilizara otro registro de uso general. Su parte más baja, AL, también tiene esa propiedad. EL registro AL es el equivalente al acumulador de los procesadores anteriores (8080 y 8085). Además hay instrucciones como DAA; DAS; AAA; AAS; AAM; AAD; LAHF; SAHF; CBW; CWD; IN y OUT que trabajan con AX o con uno de sus dos bytes (AH o AL). También se utiliza este registro junto con DX) en multiplicaciones y divisiones.

- BX.- Registro base, dividido en BH y BL.

Es el registro base y se utiliza para direccionamiento indirecto.

- CX.- Registro contador, dividido en CH y CL. Se utiliza como contador en bucles (instrucción LOOP), en operaciones con cadenas (usando el prefijo REP) y en desplazamientos y rotaciones (usando el registro CL).

- DX.- Registro de datos, dividido en DH y DL.

Se utiliza junto con el registro AX en multiplicaciones y divisiones, en la instrucción CWD y en IN y OUT para direccionamiento indirecto de puertos (el registro DX indica el número de puerto de entrada/ salida).

#### Registros del 8086

- Registros Apuntadores e Indices. Son únicamente de 16 bits de ancho y no pueden ser accedidos como byte bajo y alto. Se utilizan como apuntadores a memoria. Por ejemplo, la instrucción MOV AH, [SI] se interpreta con palabras como "Mueve el byte cuya dirección está contenida en el registro SI hacia el registro AH". SI entonces se interpreta como apuntador a la localidad de memoria deseada. Los corchetes alrededor de SI indican una dirección de memoria; esto es, son utilizados para indicar cual es el valor de dirección al que se hace referencia en la instrucción, valor apuntado por SI.

- □ SP.- Apuntador de pila (no se puede subdividir).

Aunque es un registro de uso general, debe utilizarse solo como apuntador de pila, la cual sirve para almacenar las direcciones de retorno de subrutinas y los datos temporales (mediante las instrucciones PUSH y POP). Al introducir (push) un valor en la pila este registro se decrementa en dos, mientras que al extraer (pop) un valor de la pila este registro se incrementa en dos.

- BP.- Apuntador base (no se puede subdividir). Generalmente se utiliza para realizar direccionamiento indirecto dentro de la pila.

- ☐ SI.- Apuntador índice (no se puede subdividir).

Sirve como apuntador fuente para las operaciones con cadenas.

También sirve para realizar direccionamiento indirecto.

- □ DI.- Apuntador destino ( no se puede subdividir).

Sirve como apuntador destino para las operaciones con cadenas.

También sirve para realizar direccionamiento indirecto.

- Cualquiera de estos registros puede utilizarse como fuente o destino en operaciones aritméticas y lógicas.

- □ El registro IP se incluye en el grupo de apuntadores e índices, pero este registro tiene solo una función –apuntar a la siguiente instrucción a ser buscada por la BIU. El registro IP es físicamente parte de la BIU y no bajo el control directo del programador, como en el caso de los otros registros apuntadores.

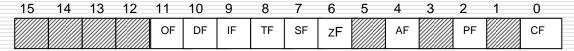

- Registro de Banderas

- □ Registro de indicadores (banderas) 16 bits

- □ CF.- (bandera de acarreo). Si vale 1, indica que hubo acarreo (en caso de suma) o préstamo (en caso de resta) desde el bit de orden más significativo del resultado. Este indicador se utiliza por instrucciones que suman o restan números que ocupan varios bytes. Las instrucciones de rotación pueden aislar un bit de la memoria o de un registro poniéndolo en el acarreo.

- PF.- (bandera de paridad). Si vale uno, el resultado tiene paridad par, es decir, un número par de bits en 1. Este indicador se puede utilizar para detectar errores de transmisión.

- AF.- (bandera auxiliar de acarreo). Si vale 1, indica que hubo arrastre o préstamo de nibble (cuatro bits) menos significativo al nibble más significativo. Este indicador se usa con las instrucciones de ajuste decimal.

- ZF.- (bandera de cero). Si este indicador vale 1, el resultado de la operación es cero.

- SF.- (bandera de signo). Refleja el bit más significativo del resultado. Como los números negativos se representan en la notación de complemento a dos, ese bit representa el signo; 0 si es positivo, si es negativo.

- OF.- (bandera de sobreflujo o desbordamiento). Si vale 1, hubo un desborde en una operación aritmética con signo, esto es, un digito significativo debido a que el tamaño del resultado es mayor que el tamaño del destino.

- TF.- (bandera de trap) Cuando TF vale 1, la CPU automáticamente genera una interrupción interna después de cada instrucción (el control se pasa a una dirección especial previamente definida por el programador), permitiendo inspeccionar los resultados del programa a medida que se ejecuta instrucción por instrucción. Normalmente, se pasa el control a un programa que despliega todos los registros y banderas del CPU. Esto se utiliza para depuración.

- IF.- (bandera de interrupción) Cuando IF se activa, la entrada de solicitud de interrupción (enmascarable) externa INTR del 8086 se habilita, esto es, ocurre una interrupción por hardware, el control será transferido a una rutina de servicio de interrupción (ISR). Cuando esta rutina haya terminado, se ejecuta una instrucción IRET (retorno de interrupción y el control será transferido se regreso a la instrucción en el programa principal que se estaba ejecutando cuando la interrupción ocurrió. Las interrupciones internas y la no enmascarable siempre se reconocen independientemente del valor de IF.

- DF.- (bandera de dirección). Esta bandera se utiliza con las instrucciones de cadena (string). Cuando DF se activa, el apuntador de memoria de cadena se decrementará automáticamente; si se pone a cero, el apuntador se incrementará.

### Registros del 8086

#### Registros de Segmento.

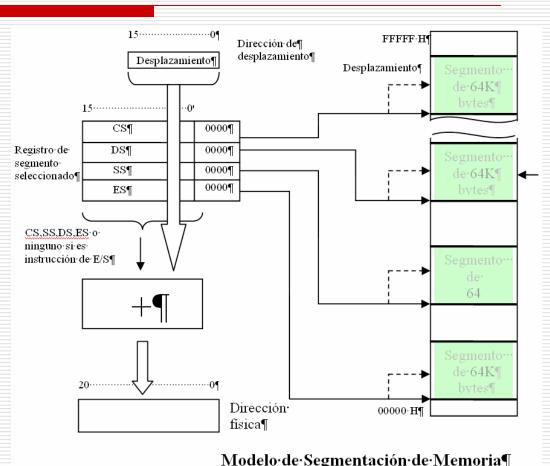

El último grupo de registros es el llamado registros de segmento. Estos registros son utilizados por la BIU para determinar la dirección de memoria de salida para el procesador cuando se va a leer o escribir a la unidad de memoria o E/S.

Los registros de segmento se llaman:

- CS: Registro de segmento de código.

- DS: Registro de segmento de datos.

- ES: Registro de segmento extra.

- SS: Registro de segmento de pila.

Estos Registros proporcionan la dirección de inicio de cada segmento.

### Memoria Segmentada

La dirección de inicio de cada segmento se obtiene multiplicando por 10H (añadiendo cuatro ceros al final) el contenido del registro de segmento correspondiente y sumando el desplazamiento, lo cual nos da una dirección de 20 bits (5 cifras hexadecimales).

Dir. real = Reg. de segmento \*10H + offset

### Memoria Segmentada

Direcciones del 8086, segmentos por default y desplazamientos

| Registro de<br>Segmento | Desplazamiento                                                         | Uso                             |

|-------------------------|------------------------------------------------------------------------|---------------------------------|

| CS                      | IP                                                                     | Dirección de instrucción        |

| SS                      | SP o BP                                                                | Dirección de pila               |

| DS                      | BX, DI (si no es instrucción de cadena),<br>SI, o un número de 16 bits | Dirección de dato               |

| ES                      | DI para instrucciones de cadena                                        | Dirección de destino de cadenas |

|                                             |                                          | Prefijo para cambiar de segmento Si se utiliza otro registro, el ensamblador genera un byte de prefijo correspondiente al segmento antes de la instrucción: |                  |                                                                                                       |                                                                                                         |  |  |

|---------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| Mnemónico<br>general<br>Op-code<br>Operando | Código<br>Objeto                         | Mnemónico Segmento de memoria Operación simbólica Descripción                                                                                               |                  |                                                                                                       |                                                                                                         |  |  |

| CS:                                         | <b>2E</b> A1 00 10<br><b>2E</b> 89 4E 00 | MOV AX, CS:MEMWCS <sup>a</sup><br>MOV CS:[BP],CX                                                                                                            | Código<br>Código | AX←CS:[1001H:1000H]<br>CS:[BP]←CX                                                                     | El segmento default para el operando de memoria fuente o destino es cambiado por el segmento de código. |  |  |

| ES:                                         | <b>26</b> A1 00 10<br><b>26</b> 89 4E 00 | MOV AX, ES:MEMWES <sup>a</sup><br>MOV ES:[BP],CX                                                                                                            | Extra<br>Extra   | AX←ES:[1001H:1000H]<br>ES:[BP+1:BP]← CX                                                               | El segmento default para el operando de memoria fuente o destino es cambiado por el segmento extra.     |  |  |

| DS:                                         | <b>3E</b> 89 4E 00                       | MOV DS:[BP],CX                                                                                                                                              | Datos            | DS:[BP+1:BP]←CX  El segmento default para el oj memoria fuente o destino es car el segmento de datos. |                                                                                                         |  |  |

| SS:                                         | <b>36</b> A1 00 10<br><b>36</b> 89 0F    | MOV AX,SS:MEMWSS <sup>a</sup><br>MOV SS:[BP],CX                                                                                                             | Pila<br>Pila     | AX←SS:[1001H:1000H]<br>SS:[BP+1:BP]←CX                                                                | El segmento default para el operando de memoria fuente o destino es cambiado por el segmento de pila.   |  |  |

<sup>&</sup>lt;sup>a</sup>El ensamblador automáticamente genera el cambio de segmento si las palabra de memoria han sido previamente definidas para asignarles otro segmento. En la tabla se asume que cada palabra empieza en la dirección 1000H en el segmento definido.

#### Modos de Direccionamiento

- Los *Modos de Direccionamiento* son las diversas formas con las que se puede indicar a un  $\mu P$  donde debe encontrar o depositar un dato, en una instrucción. Identifica los operandos de la operación a realizar, fuente y destino de los datos sobre los que se operará.

- Los operandos se pueden especificar por: un registro de la CPU, una localidad de memoria, un puerto de Entrada/Salida o un dato inmediato.

- Existen dos grupos principales según los operandos se encuentren en registros o en memoria: modos de *Registro*, y modos de *Memoria*.

- La dirección física de memoria o registro donde se encuentra realmente el operando se llama *Dirección Efectiva*, y se representa < ea >. Según el modo de direccionamiento utilizado, la CPU tendrá que realizar unos cálculos distintos hasta obtener el valor de dicha dirección efectiva.

- Las instrucciones pueden contener hasta 2 operandos que se denominan *Operando Fuente*, el del lado derecho, y *Operando Destino*, el del lado izquierdo. En estos casos, cada operando tendrá su propio modo de direccionamiento.

#### Modos de Direccionamiento

- Direccionamiento Inmediato.

- Transfiere un byte o palabra de datos inmediato hacia el operando destino. Este modo es usado para inicializar registros o localidades de memoria y para operara sobre ellos con valores constantes de datos.

- □ Ej: MOV AX,0ABCDH MOV BL,12H

- Las instrucciones que usan el modo de direccionamiento inmediato obtienen el dato como parte de la instrucción.

- B8 00 10 MOV AX,1000H

- Este modo no opera con registros de segmento, por lo que no se puede cargar un registro de segmento de manera inmediata.

#### Modos de Direccionamiento

|     |         | •            |     |          |                                    | • •   |

|-----|---------|--------------|-----|----------|------------------------------------|-------|

| 1 1 | ireccio | $n_{2}m_{1}$ | nto | nor      | $D \wedge \alpha$                  | ICTEA |

|     |         | 1141116      | -   |          | $\mathbf{R} \leftarrow \mathbf{G}$ |       |

|     |         |              |     | $\sim$ . |                                    |       |

|     |         |              |     |          |                                    |       |

- Transfiere un byte o palabra desde un registro fuente hasta un registro destino.

- □ Ej. MOV AX,CX

- □ INC BX

- El operando no requiere ninguna referencia de memoria.

Nota: Los dos operandos no pueden ser registros de segmento.

- ☐ El registro de segmento de código (CS) nunca puede utilizarse como destino.

- No se permite el acceso entre registros de segmento ni de distintos tamaños.

#### Modos de Direccionamiento

- Direccionamiento Directo.

- Transfiere un byte o palabra contenido en una localidad de memoria en el segmento DS a un registro de 8 o 16 bits. La localidad de memoria puede ser el operando fuente o destino.

- Ej: MOV AL,[1234H]

- En el modo de direccionamiento directo, la dirección de memoria se proporciona directamente como parte de la instrucción (Puede ser a través de etiquetas, en las cuales el programador no necesita conocer la dirección numérica)

- MOV AH, MEMBDS

- □ 8A 00 10 MOV AH,[MEMBDS] AH←[1000H]

#### Modos de Direccionamiento

#### Direccionamiento Indirecto.

- □ El modo de direccionamiento directo se usa para acceder localidades de memoria de manera no frecuente. Sin embargo cuando una localidad de memoria debe ser leída o escrita varias veces dentro de un programa, la búsqueda repetida de la dirección lógica hace este modo ineficiente. El modo de direccionamiento indirecto resuelve este problema almacenando esta dirección de memoria en un registro base (BX,BP)o un registro índice (SI o DI)

- MOV [DI],BH

- ☐ MOV [BP],DL

- $\square$  8B 04 MOV AX, [SI] AL $\leftarrow$ [SI]; AH $\leftarrow$ [SI+1]

- ☐ FF 25 JMP [DI] IP←[DI+1:DI]

- ☐ FE 46 00 INC BYTE PTR[BP]  $\leftarrow$  [BP]  $\leftarrow$  1

- ☐ FF OF DEC WORD PTR[BX]b  $[BX+1:BX] \leftarrow [BX+1:BX]-1$

#### Modos de Direccionamiento

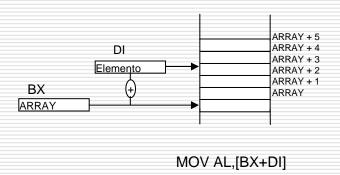

#### Direccionamiento Base mas Indice.

- Transfiere un byte o palabra entre un registro y una localidad de memoria direccionada por la suma de un registro base más un registro índice.

- Este modo es usado para el acceso a tablas.

- ☐ Ej. MOV AX,[BX+DI]

- En muchos casos, el registro base retiene la dirección de inicio de un arreglo de memoria, y el registro índice retiene la posición relativa de un dato en un arreglo.

```

8B 00 MOV AX,[BX+SI] AH\leftarrow[BX+SI+1], AL\leftarrow[BX+SI];

FF 21 JMP [BX+DI] IP\leftarrow[BX+DI+1:BX+DI];

FE 02 INC BYTE PTR[BP+SI] [BP+SI]\leftarrow[BP+SI]+1;

FF 0B DEC WORD PTR[BP+DI] [BP+DI+1:BP+DI]\leftarrow[BP+DI+1:BP+DI]-1

```

#### Modos de Direccionamiento

- □ Ej. Si se desea direccionar los elementos en un arreglo de datos localizados en el segmento de datos en la localidad ARRAY. Se requiere cargar BX con la dirección ARRAY y DI con el número del elemento del arreglo que se desea acceder.

- MOV BX, OFFSET ARRAY

- MOV DI,3

- MOV AL,[BX+DI]

#### Modos de Direccionamiento

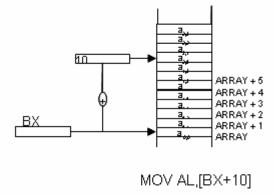

#### Direccionamiento Relativo a Registro

- Transfiere un byte o palabra entre un registro y una localidad de memoria direccionada por un registro base o un registro índice más un desplazamiento.

- Si la localidad de memoria se direcciona por la suma de un registro base y un desplazamiento, también se conoce como direccionamiento basado.

- □ Ej. MOV AX,[BX+10H]

- Si la localidad de memoria se direcciona por la suma de un registro índice y un desplazamiento, también se conoce como direccionamiento indexado.

- □ Ej. MOV AX,[SI+500H]

- MOV AX,[BX+4]

- MOV AX, ARRAY [SI]

- MOV LIST[BP],CL

- MOV ARRAY[DI],AL

Modos de Direccionamiento

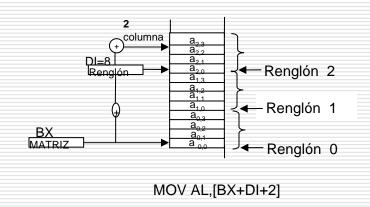

- Direccionamiento Relativo Base más índice.

- Transfiere un byte o palabra entre un registro y la localidad de memoria direccionada por un registro base más un registro índice más un desplazamiento.

- □ Ej. MOV AX, [BX+SI+100H]

- MOV AX, ARRAY[BX+DI]

- MOV LIST[BP+DI],CL

#### Modos de Direccionamiento

Este tipo de

direccionamiento es usado comúnmente para direccionar arreglos de datos en memoria de dos dimensiones (matrices).

Selecciona elemento a22

MOV BX, OFFSET MATRIZ MOV DI,8 MOV AL,[BX+DI+2]

$$\left[\begin{array}{cccc} a_{0,0} & a_{0,1} & a_{0,2} & a_{0,3} \\ a_{1,0} & a_{1,1} & a_{1,2} & a_{1,3} \\ a_{2,0} & a_{2,1} & a_{2,2} & a_{2,3} \end{array}\right]$$

#### Modos de Direccionamiento

#### Modo de direccionamiento de string

- En computación un string (cadena) es una secuencia de bytes o palabras almacenadas en memoria. Una tabla de datos es un ejemplo de string. Debido a su importancia el 8086 tiene algunas instrucciones diseñadas específicamente para manejar strings (cadenas) de caracteres.

- Estas instrucciones tienen un modo de direccionamiento especial y usan a DS:SI para apuntar al string fuente y a ES:DI para apuntar al string destino.

- MOVSB mueve el byte del dato fuente a la localidad destino. SI y DI se incrementan o decrementan automáticamente dependiendo del valor de la bandera D.

#### **Modos de Direccionamiento**

|                                             |                  | Instrucciones de Cadena (string) |                        |                                                                       |                                                                                                                  |  |  |

|---------------------------------------------|------------------|----------------------------------|------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| Mnemónico<br>general<br>Op-code<br>Operando | Código<br>Objeto | Mnemónico                        | Segmento<br>de memoria | Operación<br>simbólica                                                | Descripción                                                                                                      |  |  |

| STOSB                                       | AA               | STOSB                            | Extra                  | ES:[DI]←AL<br>Si DF=0, DI←DI+1<br>Si DF=1, DI←DI-1                    | Transfiere un byte o palabra del registro AL o AX a la cadena direccionada por DI en el segmento extra; Si DF=0, |  |  |

| STOSW                                       | AB               | STOSW                            | Extra                  | ES:[DI] ← AL<br>ES:[DI+1] ←AH<br>Si DF=0, DI←DI+2<br>Si DF=1, DI←DI-2 | incrementa DI, de lo contrario<br>decrementa DI; las banderas no son<br>afectadas.                               |  |  |

| LODSB                                       | AC               | LODSB                            | Datos                  | AL← DS:[SI]<br>Si DF=0,SI←SI+1<br>Si DF=1, SI←SI-1                    | Transfiere un byte o palabra de la cadena direccionada por SI en el segmento de datos al registro AL o AX;       |  |  |

| LODSW                                       | AD               | LODSW                            | Datos                  | AL←DS:[SI]<br>AH←DS:[SI+1]<br>Si DF=0, SI←SI+2<br>Si DF=1, SI←SI-2    | Si DF=0, incrementa SI, de lo contrario decrementa SI; las banderas no son afectadas.                            |  |  |

### Tema 2. Características del Microprocesador 80X86. Modos de Direccionamiento

| Direccionamiento         | Cod. Ob.                                     | Mnemónico                                                                           | Segmento                         | Operación simbólica                                                                                                  |

|--------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Inmediato                | B8 00 10                                     | MOV AX,1000H                                                                        | Código                           | AH←10H; AL <b>←</b> 00                                                                                               |

| Registro                 | 8B D1                                        | MOV DX,CX                                                                           | Dentro del CPU                   | DX←CX                                                                                                                |

| Directo                  | 8A 00 10                                     | MOV AH,[MEMBDS]                                                                     | Datos                            | AH←[1000H]                                                                                                           |

| Indirecto a registro     | 8B 04<br>FF 25<br>FE 46 00<br>FF 0F          | MOV AX, [SI] JMP [DI] INC BYTE PTR[BP] DEC WORD PTR[BX]                             | Datos<br>Datos<br>Stack<br>Datos | AL←[SI]; AH←[SI+1] IP←[DI+1:DI] [BP]←[BP] + 1 [BX+1:BX]←[BX+1:BX]-1                                                  |

| Indexado                 | 8B 44 06<br>FF 65 06                         | MOV AX,[SI+6]<br>JMP [DI+6]                                                         | Datos<br>Datos                   | AL←[SI+6]; AH←[SI+7]<br>IP ← [DI+7:DI+6]                                                                             |

| Basado                   | 8B 46 02<br>FF 67 02                         | MOV AX,[BP+2]<br>JMP [BX+2] <sup>c</sup>                                            | Stack<br>Datos                   | AL←[BP+2]; AH←[BP+3]<br>IP←[BX+3:BX+2]                                                                               |

| Base mas índice          | 8B 00<br>FF 21<br>FE 02<br>FF 0B             | MOV AX,[BX+SI] JMP [BX+DI] INC BYTE PTR[BP+SI] DEC WORD PTR[BP+DI]                  | Datos<br>Datos<br>Stack<br>Stack | AL←[BX+SI]; AH←[BX+SI+1] IP←[BX+DI+1:BX+DI] [BP+SI]←[BP+SI]+1 [BP+DI+1:BP+DI]←[BP+DI+1:BP+DI]-1                      |

| Relativo base mas índice | 8B 40 05<br>FF 61 05<br>FE 42 05<br>FF 4B 05 | MOV AX,[BX+SI+5]<br>JMP [BX+DI+5]<br>INC BYTE PTR[BP+SI+5]<br>DEC WORD PTR[BP+DI+5] | Datos<br>Datos<br>Stack<br>Stack | AL←[BX+SI+5]; AH←[BX+SI+6]<br>IP←[BX+DI+6:BX+DI+5]<br>[BP+SI+5]←[BP+SI+5]+1<br>[BP+DI+6:BP+DI+5]←[BP+DI+6:BP+DI+5]-1 |

| String                   | A4                                           | MOVSB                                                                               | Extra, Datos                     | ES:[DI]←DS:[SI] Si DF=0, entonces SI←SI+1; DI←DI+1 Si DF=1, entonces SI←SI-1; DI←DI-1                                |

### Conjunto de Instrucciones del 8086

| Mnemónico        | Código Objeto     | Mnemónico        | Segmento de<br>memoria | Operación simbólica              |

|------------------|-------------------|------------------|------------------------|----------------------------------|

| MOV dest, fuente | 8B C3             | MOV AX,BX        | Dentro del CPU         | AX←BX                            |

|                  | 8A E3             | MOV AH,BL        | Dentro del CPU         | AH←BL                            |

|                  | A1 00 10          | MOV AX,MEMWDS    | Datos                  | AL <b>←</b> [1000H],             |

|                  |                   |                  |                        | AH <b>←</b> [1001H]              |

|                  | A0 02 10          | MOV AL, MEMBDS   | Datos                  | AL <b>←</b> [1002H]              |

|                  | 89 1E 00 10       | MOV MEMWDS,BX    | Datos                  | [1000H]←BL,                      |

|                  |                   |                  |                        | [1001H] <b>←</b> BH              |

|                  | 88 1E 02 10       | MOV MEMBDS,BL    | Datos                  | [1002H]←BL                       |

|                  | C7 06 00 10 34 12 | MOV MEMWDS,1234H | Datos                  | [1000H] <b>←</b> 34H,            |

|                  |                   |                  |                        | [1001H] <b>←</b> 12H             |

|                  | C6 06 02 10 34    | MOV MEMBDE,34H   | Datos                  | [1002H] <b>←</b> 34H             |

|                  | B0 10             | MOV AL,10H       | Código                 | AL <b>←</b> 10H                  |

|                  | B8 00 10          | MOV AX,1000H     | Código                 | A1 <b>←</b> 00H, AH <b>←</b> 10H |

|                  | 8E D8             | MOV DS,AX        | Dentro del CPU         | DS←AX                            |

|                  | 8C C2             | MOV DX,ES        | Dentro del CPU         | DX←ES                            |

|                  | 8E 06 00 10       | MOV ES,MEMWDS    | Datos                  | ES <b>←</b> [1001H:1000H]        |

|                  | 8C 0E 00 10       | MOV MEMWDS,CS    | Datos                  | [1001H:1000H]←CS                 |

#### Instrucciones de Transferencia de datos especiales

| Mnemónico                                                 | Código<br>Objeto           | Mnemónico                                          | Segmento de<br>memoria                    | Operación simbólica                                                                                          |

|-----------------------------------------------------------|----------------------------|----------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| XCHG dest, fuente                                         | 93<br>86 C7<br>87 14       | XCHG AX,BX<br>XCHG AL,BH<br>XCHG [SI],DX           | Dentro del CPU<br>Dentro del CPU<br>Datos | $AX \rightleftharpoons BX$ $AL \rightleftharpoons BH$ $[SI] \rightleftarrows DL; [SI+1] \rightleftarrows DH$ |

| LAHF                                                      | 9F                         | LAHF                                               | Dentro del CPU                            | AH ← Banderas                                                                                                |

| SAHF                                                      | 9E                         | SAHF                                               | Dentro del CPU                            | Banderas ← AH                                                                                                |

| IN acumulador, puerto                                     | E4 26<br>E5 26<br>EC<br>ED | IN AL,26H<br>IN AX,26H<br>IN AL,DX<br>IN AX,DX     | b b b b                                   | AL← puerto 26H<br>AL←puerto 26H, AH←puerto 27H<br>AL←puerto DX<br>AL← puerto DX; AH←puerto DX+1              |

| OUT puerto,acumulador                                     | E6 26<br>E7 26<br>EE<br>EF | OUT 26H,AL<br>OUT 26H,AX<br>OUT DX,AL<br>OUT DX,AX | b b b b                                   | puerto 26H←AL<br>puerto 26H←AL; puerto 27H←AH<br>puerto DX←AL<br>puerto DX←AL; puerto DX+1 ←AH               |

| LEA dest,fuente <sup>c</sup>                              | 8D 1E 00 10                | LEA BX,MEMBDS                                      | Datos                                     | BL←00; BH ←10H                                                                                               |

| LDS dest,fuente <sup>d</sup> LES dest,fuente <sup>d</sup> | C5 1C<br>C4 1C             | LDS BX,DWORD PTR[SI] LES BX,DWORD PTR[SI]          | Datos<br>Datos                            | BL ←[SI]; BH←[SI+1];<br>DS←[SI+3:SI+2]<br>BL ←[SI]; BH←[SI+1];<br>ES←[SI+3:SI+2]                             |

| XLAT                                                      | D7                         | XLAT                                               | Datos                                     | AL←[BX+AL];                                                                                                  |

#### Instrucciones de cadena

| Mnemónico | Código Objeto | Mnemónico | Segmento     | Operación simbólica                                                                    |

|-----------|---------------|-----------|--------------|----------------------------------------------------------------------------------------|

| STOSB     | AA            | STOSB     | Extra        | ES:[DI]←AL<br>Si DF=0, DI←DI+1<br>Si DF=1, DI←DI-1                                     |

| STOSW     | AB            | STOSW     | Extra        | ES:[DI] ← AL; ES:[DI+1] ← AH<br>Si DF=0, DI←DI+2<br>Si DF=1, DI←DI-2                   |

| LODSB     | AC            | LODSB     | Datos        | AL← DS:[SI] Si DF=0,SI←SI+1 Si DF=1, SI←SI-1                                           |

| LODSW     | AD            | LODSW     | Datos        | AL←DS:[SI]; AH←DS:[SI+1]<br>Si DF=0, SI←SI+2<br>Si DF=1, SI←SI-2                       |

| MOVSB     | A4            | MOVSB     | Datos, Extra | ES:[DI] ← DS:[SI] Si DF=0,DI←DI+1, SI←SI+1 Si DF=1, DI←DI-1, SI←SI-1                   |

| MOVSW     | A5            | MOVSW     | Datos, Extra | ES:[DI+1 :DI] ← DS:[SI+1: SI]<br>Si DF=0,DI←DI+2, SI←SI+2 Si DF=1,<br>DI←DI-2, SI←SI-2 |

#### Instrucciones de cadena

| Mnemónico      | Código Objeto                    | Mnemónico                                        | Segmento                              | Operación simbólica                                                                                                                                                   |

|----------------|----------------------------------|--------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCASB          | AE                               | SCASB                                            | Extra                                 | AL – ES:[DI]; actualiza banderas<br>Si DF=0, DI← DI + 1<br>Si DF=1, DI← DI - 1                                                                                        |

| SCASW          | AF                               | SCASW                                            | Extra                                 | AX – ES:[DI+1:DI]; actualiza banderas<br>Si DF=0, DI← DI + 2<br>Si DF=1, DI← DI - 2                                                                                   |

| CMPSB          | A6                               | CMPSB                                            | Extra, Datos                          | DS:[SI] - ES:[DI]; actualiza banderas<br>Si DF=0 DI←DI+1, SI←SI+1<br>Si DF=1 DI←DI-1, SI←SI-1                                                                         |

| CMPSW          | A7                               | CMPSW                                            | Extra, Datos                          | DS:[SI+1:SI] - ES:[DI+1:DI]; actualiza banderas<br>Si DF=0 DI←DI+2, SI←SI+2<br>Si DF=1 DI←DI-2, SI←SI-2                                                               |

| Prefijo<br>REP |                                  |                                                  |                                       |                                                                                                                                                                       |

| REP            | F3 AA<br>F3 AB<br>F3 A4<br>F3 A5 | REP STOSB<br>REP STOSW<br>REP MOVSB<br>REP MOVSW | Extra Extra Extra, datos Extra, datos | STOSB; CX← CX – 1 Repite hasta que CX=0<br>STOSW; CX← CX – 1 Repite hasta que CX=0<br>MOVSB; CX← CX – 1 Repite hasta que CX=0<br>MOVSW; CX←CX-1 Repite hasta que CX=0 |

### Tema 2. Características del Microprocesador 80X86. Instrucciones de cadena (Prefijo de repetición)

| Mnemónico   | Código<br>Objeto                 | Mnemónico                                            | Segmento                        | Operación simbólica                                                                                                                                                                 |

|-------------|----------------------------------|------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REP         | F3 AA<br>F3 AB<br>F3 A4<br>F3 A5 | REP STOSB<br>REP STOSW<br>REP MOVSB<br>REP MOVSW     | Extra Extra, datos Extra, datos | STOSB; CX← CX – 1 Repite hasta que CX=0<br>STOSW; CX← CX – 1 Repite hasta que CX=0<br>MOVSB; CX← CX – 1Repite hasta que CX=0<br>MOVSW; CX←CX-1Repite hasta que CX=0                 |

| REPE/REPZ   | F3 AE<br>F3 AF<br>F3 A6<br>F3 A7 | REPZ SCASB<br>REPZ SCASW<br>REPZ CMPSB<br>REPZ CMPSW | Extra Extra, datos Extra, datos | SCASB; CX ← CX – 1 Repite si ZF = 1 y CX ≠ 0 Similar a la anterior excepto SCASW Similar a la anterior excepto CMPSB Similar a la anterior excepto CMPSW                            |

| REPNE/REPNZ | F2 AE<br>F2 AF<br>F2 A6<br>F2 A7 | REPNE SCASB REPNE SCASW REPNE CMPSB REPNE CMPSW      | Extra Extra, datos Extra, datos | SCASB; $CX \leftarrow CX - 1$ Repite si $ZF = 0$ y $CX \neq 0$<br>Similar a la anterior excepto SCASW<br>Similar a la anterior excepto CMPSB<br>Similar a la anterior excepto CMPSW |

#### Instrucciones de Corrimiento y Rotación

| Mnemónico                          | Código Objeto  | Mnemónico                                 | Segmento de<br>memoria           | Operación simbólica                |

|------------------------------------|----------------|-------------------------------------------|----------------------------------|------------------------------------|

| SAL/SHL <sup>b</sup> dest,contador | D1 E0<br>D3 E0 | SAL AX,1<br>SAL AX,CL                     | Dentro del CPU<br>Dentro del CPU | <b>□</b> ◆ <b>₽</b>           •• 0 |

| SAR dest, contador                 | D0 F8<br>D2 F8 | SAR AL,1<br>SAR AL,CL                     | Dentro del CPU<br>Dentro del CPU |                                    |

| SHR dest, contador                 | D1 2C<br>D2 2C | SHR WORD PTR[SI],1<br>SHR BYTE PTR[SI],CL | Datos<br>Datos                   |                                    |

| RCL dest, contador                 | D1 D3<br>D3 D3 | RCL BX,1<br>RCL BX,CL                     | Dentro del CPU<br>Dentro del CPU |                                    |

| RCR dest, contador                 | D0 DB<br>D2 DB | RCR BL,1<br>RCR BL,CL                     | Dentro del CPU<br>Dentro del CPU |                                    |

| ROL dest, contador                 | D1 04<br>D2 04 | ROL WORD PTR[SI],1<br>ROL BYTE PTR[SI],CL | Datos<br>Datos                   | □ <b>◆₽</b> ↓↓↓↓↓                  |

ROR MEMWDS,1

ROR MEMBDS,CL

Datos

Datos

D1 0E 00 10

D2 0E 04 10

ROR dest, contador

### Tema 2. Características del Microprocesador 80X86. Instrucciones Lógicas

| Mnemónico<br><sub>[SX]</sub> € | Código<br>Objeto | Mnemónico <sup>a</sup> | Segmento de<br>memoria | Operación simbólica             |

|--------------------------------|------------------|------------------------|------------------------|---------------------------------|

| NOT dest                       | F7 D3            | NOT BX                 | Dentro del CPU         | BX←BX′                          |

|                                | F6 14            | NOT BYTE PTR[SI]       | Datos                  | [SI] ← [SI]′                    |

| AND dest, fuente               | 23 CA            | AND CX, DX             | Dentro del CPU         | CX ← CX ^ DX                    |

|                                | 22 3C            | AND BH,BYTE PTR [SI]   | Datos                  | BH ← BH ^ [SI]                  |

|                                | 25 00 80         | AND AX, 8000H          | Código                 | AX ← AX ^ 8000H                 |

| OR dest, fuente                | 0B CA            | OR CX,DX               | Dentro del CPU         | $CX \leftarrow CX + DX$         |

|                                | 0A 3C            | OR BH, BYTE PTR[SI]    | Datos                  | $BH \leftarrow BH + [SI]$       |

|                                | 0D 00 80         | OR AX,8000H            | Código                 | $AX \leftarrow AX + 8000H$      |

| XOR dest, fuente               | 33 CA            | XOR CX,DX              | Dentro del CPU         | $CX \leftarrow CX \oplus DX$    |

|                                | 32 3C            | XOR BH, BYTE PTR[SI]   | Datos                  | $BH \leftarrow BH \oplus [SI]$  |

|                                | 35 00 80         | XOR AX,8000H           | Código                 | $AX \leftarrow AX \oplus 8000H$ |

| TEST dest, fuente              | 85 D1            | TEST CX,DX             | Dentro del CPU         | CX ^ DX; actualiza banderas     |

|                                | 84 3C            | TEST BH, BYTE PTR[SI]  | Datos                  | BH ^ [SI]; actualiza banderas   |

|                                | A9 00 80         | TEST AX,8000H          | Código                 | AX ^ 8000H; actualiza banderas  |

#### Instrucciones de Adición y Substracción

| Mnemónico        | Código Objeto                                      | Mnemónico <sup>a</sup>                | Segmento de<br>memoria | Operación simbólica                                                                                     |

|------------------|----------------------------------------------------|---------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------|

| ADD dest, fuente | 03 F2<br>00 2F<br>81 C7 00 80<br>81 06 00 10 00 80 | ADD BYTE PTR[BX],CH<br>ADD DI,8000H   | Datos                  | SI ← SI + DX<br>[BX]←[BX] + CH<br>DI← DI + 8000H<br>[1001H:1000H]← [1001H:1000H]+8000H                  |

| ADC dest, fuente | 13 F2<br>10 2F<br>81 D7 00 80<br>81 16 00 10 00 80 | ADC BYTE PTR [BX],CH<br>ADC DI, 8000H | Datos                  | SI ← SI + DX + CF<br>[BX]←[BX]+CH + CF<br>DI← DI + 8000H + CF<br>[1001H:1000H]← [1001H:1000H]+8000H+CF  |

| SUB dest, fuente | 2B F2<br>28 2F<br>81 EF 00 80<br>81 2E 00 10 00 80 | SUB BYTE PTR[BX],CH<br>SUB DI,8000H   | Datos                  | SI ← SI - DX<br>[BX]←[BX] - CH<br>DI← DI - 8000H<br>[1001H:1000H]← [1001H:1000H]-8000H                  |

| SBB dest, fuente | 1B F2<br>18 2F<br>81 DF 00 80<br>81 1E 00 10 00 80 | SBB BYTE PTR [BX],CH<br>SBB DI, 8000H | Datos                  | SI ← SI - DX - CF<br>[BX]←[BX]- CH - CF<br>DI← DI - 8000H - CF<br>[1001H:1000H]← [1001H:1000H]-8000H-CF |

|                                                 |                                                       | Ejemplo codificado                                                       |                                           |                                                                                                                                |

|-------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Mnemónico<br>general<br>Op-code<br>Operan<br>do | Código Objeto                                         | Mnemónico <sup>a</sup>                                                   | Segmento de<br>memori<br>a                | Operación simbólica                                                                                                            |

| INC dest <sup>b</sup>                           | FE C3                                                 | INC BL                                                                   | Dentro del CPU                            | BL←BL+1                                                                                                                        |

|                                                 | FF 05                                                 | INC WORD PTR[DI]                                                         | Datos                                     | [DI+1:DI]←[DI+1:DI]+1                                                                                                          |

|                                                 | FE 06 04 10                                           | INC MEMBDS°                                                              | Datos                                     | [1004H]← [1004H]+1                                                                                                             |

| DEC dest <sup>b</sup>                           | FE CB                                                 | DEC BL                                                                   | Dentro del CPU                            | BL←BL-1                                                                                                                        |

|                                                 | FF 0D                                                 | DEC WORD PTR[DI]                                                         | Datos                                     | [DI+1:DI]←[DI+1:DI]-1                                                                                                          |

|                                                 | FE 0E 04 10                                           | DEC MEMBDS <sup>c</sup>                                                  | Datos                                     | [1004H]← [1004H]-1                                                                                                             |

| NEG dest <sup>b</sup>                           | F6 DB                                                 | NEG BL                                                                   | Dentro del CPU                            | BL←0 - BL                                                                                                                      |

|                                                 | F7 1D                                                 | NEG WORD PTR[DI]                                                         | Datos                                     | [DI+1:DI]← 0 - [DI+1:DI]                                                                                                       |

|                                                 | F6 1E 04 10                                           | NEG MEMBDS <sup>c</sup>                                                  | Datos                                     | [1004H]← 0 - [1004H]                                                                                                           |

| CMP dest,<br>fuente                             | 3A C4<br>39 0D<br>81 3E 00 10 00<br>80<br>81 FF 00 80 | CMP AL,AH<br>CMP [DI],CX<br>CMP MEMWDS,800H <sup>a</sup><br>CMP DI,8000H | Dentro del CPU Datos Datos Dentro del CPU | AL – AH; actualiza banderas [DI+1:DI]-CX; actualiza bandera [1001H:1000H]-8000H;actualiza banderas DI-8000H;actualiza banderas |

#### Instrucciones de Multiplicación y División.

| Mnemónico   | Código<br>Objeto                       | Mnemónico                                     | Segmento de<br>memoria                             | Operación simbólica                                                                                                             |

|-------------|----------------------------------------|-----------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| MUL fuente  | F6 E3<br>F7 E1<br>F6 27<br>F7 26 00 10 | MUL BL MUL CX MUL BYTE PTR[BX] MUL MEMWDS     | Dentro del CPU<br>Dentro del CPU<br>Datos<br>Datos | $AX \leftarrow AL * BL$<br>$DX:AX \leftarrow AX * CX$<br>$AX \leftarrow AL * [BX]$<br>$DX:AX \leftarrow AX * [1001H:1000H]$     |

| IMUL fuente | F6 EB<br>F7 E9<br>F6 2F<br>F7 2E 00 10 | IMUL BL IMUL CX IMUL BYTE PTR[BX] IMUL MEMWDS | Dentro del CPU<br>Dentro del CPU<br>Datos<br>Datos | AX ← AL * BL (con signo)  DX:AX←AX * CX (con signo)  AX← AL * [BX] (con signo)  DX:AX←AX* [1001H:1000H] (con signo)             |

| DIV         | F6 F3<br>F7 F1<br>F6 37<br>F7 36 00 10 | DIV BL DIV CX DIV BYTE PTR[BX] DIV MEMWDS     | Dentro del CPU<br>Dentro del CPU<br>Datos<br>Datos | $AX \leftarrow AX / BL$<br>$DX:AX \leftarrow DXAX / CX$<br>$AX \leftarrow AX / [BX]$<br>$DX:AX \leftarrow DXAX / [1001H:1000H]$ |

| IDIV        | F6 FB<br>F7 F9<br>F6 3F<br>F7 3E 00 10 | IDIV BL IDIV CX IDIV BYTE PTR[BX] IDIV MEMWDS | Dentro del CPU<br>Dentro del CPU<br>Datos<br>Datos | AX ← AX / BL (con signo)  DX:AX←DXAX / CX (con signo)  AX← AX / [BX] (con signo)  DX:AX←DXAX /[1001H:1000H] (con signo)         |

Instrucciones de Ajuste.

| Mnemónico | Código<br>Objeto | Mnemó-<br>nico | Segmento de memoria | Operación simbólica                                                                                                                                                  |

|-----------|------------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAA       | 27               | DAA            | Dentro del CPU      | Si AL $\wedge$ 0F > 9 o AF = 1, entonces<br>AL $\leftarrow$ AL+6; AF $\leftarrow$ 1<br>Si AL > 9F o CF = 1, entonces AL $\leftarrow$ AL+60H; CF $\leftarrow$ 1       |

| DAS       | 2F               | DAS            | Dentro del CPU      | Si AL $\wedge$ 0F > 9 o AF = 1, entonces<br>AL $\leftarrow$ AL-6; AF $\leftarrow$ 1<br>Si AL > 9F o CF = 1, entonces AL $\leftarrow$ AL - 60H; CF $\leftarrow$ 1     |

| AAA       | 37               | AAA            | Dentro del CPU      | Si AL $\wedge$ 0F > 9 o AF = 1, entonces<br>AL $\leftarrow$ AL + 6; AH $\leftarrow$ AH + 1; AF $\leftarrow$ 1; CF $\leftarrow$ AF;<br>AL $\leftarrow$ AL $\wedge$ 0F |

| AAS       | 3F               | AAS            | Dentro del CPU      | Si AL $\wedge$ 0F > 9 o AF = 1, entonces<br>AL $\leftarrow$ AL - 6; AH $\leftarrow$ AH - 1; AF $\leftarrow$ 1; CF $\leftarrow$ AF;<br>AL $\leftarrow$ AL $\wedge$ 0F |

| AAM       | D4 0A            | AAM            | Dentro del CPU      | $AH \leftarrow AL / 0AH$ $AL \leftarrow Residuo$                                                                                                                     |

| AAD       | D5 0A            | AAD            | Dentro del CPU      | $AL \leftarrow (AH * 0AH) + AL \qquad AH \leftarrow 0$                                                                                                               |

| CBW       | 98               | CBW            | Dentro del CPU      | Si AL < 80H, entonces AH ← 0<br>Si AL > 7F, entonces AH ← FFH                                                                                                        |

| CWD       | 99               | CWD            | Dentro del CPU      | Si AX < 8000H, entonces DX ← 0 Si AX > 7FFFFH, entonces DX ← FFFFH                                                                                                   |

### Instrucciones de Ajuste.

```

□ DAA (decimal adjust after addition)

mov al,35h

add al,48h; AL=7DH

daa ; AL=83H

□ DAS (decimal adjust after substraction)

mov bl,48h

mov al,85h ;

sub al, bl ; AL=3DH

das ; AL=37H

```

### Instrucciones de Ajuste.

AAA(ASCII adjust after addition)

```

mov ah,0

mov al,'8' ; AX=0038H

add al,'2' ; AX=006AH

aaa ; AX=0100H

or ax,3030h ; AX=3130H='10'

```

□ AAS (ASCII adjust after substraction) Ajusta el resultado binario obtenido de una instrucción SUB o SBB. Provoca que el resultado en AL sea consistente con una representación ascii. Por ejemplo, el siguiente fragmento de código resta el ascii 9 del ascii 8, en donde después de la instrucción SUB, AX es igual a 00FFh (-1) y la instrucción AAS convierte AX a FF09, el complemento a 10 de -1.

```

Datos segment

val1 db '8'

val2 db '9'

Datos ends

Codigo segment 'code'

mov ah,0

mov al,val1 ; AX=0038H

sub al,val2 ; AX=FF09H

aas ; AX=FF09H

```

#### Instrucciones de Ajuste.

### AAM (ASCII adjust after multiplication)

```

Datos segment

ascVal db 05h,06h

Datos ends

```

Codigo segment

i

mov bl,ascVal ;primer operando

mov al,ascVal; segundo operando

mul bl ;AX=001EH

aam ;AX=0300H

or ax,3030h; AX=3330H='30'

### AAD (ASCII adjust before division)

Datos segment

cociente db?

residuo db?

Datos ends

Codigo segment

i

mov ax,0307H ;dividendo (BCD)

aad ;AX=0025H (AH\*10+AL)

mov bl,05 ;divisor

div bl ;AX=0207H

mov cociente,al

mov residuo, ah

### Tema 2. Características del Microprocesador 80X86. Instrucciones de Salto.

| Mnemónico             | Código Objeto                          | Mnemónico                                              | Segmento                                   | Operación simbólica                                                                       |

|-----------------------|----------------------------------------|--------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|

| JMP near etiqueta     | E9<br>FF 26 00 10<br>FF 27<br>FF E0    | JMP MEMN JMP [MEMWDS] JMP [BX] JMP AX                  | Código<br>Datos<br>Datos<br>Dentro del CPU | IP← MEMN IP←[MEMWDS+1:MEMWDS] IP←[BX+1:BX] IP←AX                                          |

| JMP SHORT etiqueta    | EB                                     | JMP SHORT MEMS                                         | Código                                     | IP←MEMS                                                                                   |

| JMP far etiqueta      | EA 03 00 D3 9E<br>FF 2E 05 10<br>FF 2F | JMP FAR PTR MEMF<br>JMP [MEMWWDS]<br>JMP DWORD PTR[BX] | Código<br>Datos<br>Datos                   | IP←0003H; CS-←9ED3H<br>IP←[1006H:1005H]; CS←[1008H:1007H]<br>IP←[BX+1:BX]; CS←[BX+3:BX+2] |

| Jcondh short etiqueta | 73                                     | JNC MEMS                                               | Código                                     | Si CF=0, entonces IP←MEMS                                                                 |

| JCXZ short etiqueta   | Е3                                     | JCXZ MEMS                                              | Código                                     | Si CX=0, entonces IP←MEMS                                                                 |

#### Instrucciones de Salto Condicional.

| Saltos Condicionales para i | Saltos Condicionales para números con signo y sin signo |           |  |  |  |  |

|-----------------------------|---------------------------------------------------------|-----------|--|--|--|--|

| Mnemónico                   | Significado                                             | Condición |  |  |  |  |

|                             |                                                         |           |  |  |  |  |

| JE / JZ                     | Salta si es igual o salta si es cero                    | ZF = 1    |  |  |  |  |

| JNE / JNZ                   | Salta si no es igual o salta si no es cero              | ZF = 0    |  |  |  |  |

| JC                          | Salta si hay acarreo                                    | CF = 1    |  |  |  |  |

| JNC                         | Salta si no hay acarreo                                 | CF = 0    |  |  |  |  |

| JS                          | Salta si el signo es negativo                           | SF = 1    |  |  |  |  |

| JNS                         | Salta si el signo es positivo                           | SF = 0    |  |  |  |  |

| JO                          | Salta si hay desbordamiento (sobreflujo)                | OF = 1    |  |  |  |  |

| JNO                         | Salta si no hay desbordamiento (sobreflujo)             | OF = 0    |  |  |  |  |

| JP / JPE                    | Salta si hay paridad o salta si la paridad es par       | PF = 1    |  |  |  |  |

| JNP / JPO                   | Salta si no hay paridad o salta si la paridad es impar  | PF = 0    |  |  |  |  |

#### Instrucciones de Salto Condicional.

| Saltos Condicionales para números sin signo |                                                  |                              |  |  |  |  |

|---------------------------------------------|--------------------------------------------------|------------------------------|--|--|--|--|

| Mnemónico                                   | Significado                                      | Condición                    |  |  |  |  |

| JA / JNBE                                   | Salta si es mayor o salta si no es menor igual   | CF = 0 y $ZF = 0$            |  |  |  |  |

| JAE / JNB                                   | Salta si es mayor o igual o salta si no es menor | CF = 0                       |  |  |  |  |

| JB / JNAE                                   | Salta si es menor o salta si no es mayor igual   | CF = 1                       |  |  |  |  |

| JBE / JNA                                   | Salta si es menor o igual o salta si no es mayor | CF = 1  o  Z = 1             |  |  |  |  |

|                                             |                                                  |                              |  |  |  |  |

| Saltos Condicionales                        | s para números con signo                         |                              |  |  |  |  |

| Mnemónico                                   | Significado                                      | Condición                    |  |  |  |  |

| JG / JNLE                                   | Salta se es mayor o salta si no es menor igual   | ZF = 0 y $SF = OF$           |  |  |  |  |

| JGE / JNL                                   | Salta si es mayor o igual o salta si no es menor | SF = OF                      |  |  |  |  |

| JL / JNGE                                   | Salta si es menor o salta si no es mayor igual   | (SF □ OF)=1                  |  |  |  |  |

| JLE / JNG                                   | Salta si es menor o igual o salta si no es mayor | $((SF \square OF) + ZF) = 1$ |  |  |  |  |

#### Instrucciones de Salto Condicional.

| Mnemónico                         | Código<br>Objeto | Mnemónicoa               | Segmento | Operación simbólica                                                                    |

|-----------------------------------|------------------|--------------------------|----------|----------------------------------------------------------------------------------------|

| LOOP etiqueta corta               | E2a              | LOOP MEMS <sup>b</sup>   | Código   | $CX \leftarrow CX - 1$<br>Si $CX \neq 0$ , entonces IP $\leftarrow$ MEMS               |

| LOOPE / etiqueta corta<br>LOOPZ   | E1a              | LOOPZ MEMS <sup>b</sup>  | Código   | $CX \leftarrow CX - 1$<br>Si $(CX \neq 0)^{(ZF=1)}$ , entonces<br>IP $\leftarrow$ MEMS |

| LOOPNE / etiqueta corta<br>LOOPNZ | E0a              | LOOPNZ MEMS <sup>b</sup> | Código   | $CX \leftarrow CX - 1$<br>Si $(CX \neq 0)^{(ZF=0)}$ , entonces<br>IP $\leftarrow$ MEMS |

#### Instrucciones de Llamado a Subrutina.

| Mnemónico general<br>Op-code Operando | Código Objeto | Mnemónico     | Segmento       | Operación simbólica                              |

|---------------------------------------|---------------|---------------|----------------|--------------------------------------------------|

| CALL etiqueta cercana                 | E8            | CALL MEMN     | Código         | SP← SP -2;<br>[SP+1:SP]← IP;<br>IP← MEMN         |

|                                       | FF 16 00 10   | CALL [MEMWDS] | Datos          | SP← SP -2;<br>[SP+1:SP]← IP;<br>IP←[1001H:1000H] |

|                                       | FF15          | CALL [DI]     | Datos          | SP← SP -2;<br>[SP+1:SP]← IP;<br>IP←[DI+1:DI]     |

|                                       | FF D7         | CALL DI       | Dentro del CPU | SP← SP -2;<br>[SP+1:SP]← IP;<br>IP←DI            |

#### Instrucciones de Llamado a Subrutina (cont.)

| Mnemónico            | Código Objeto  | Mnemónico          | Segmento | Operación simbólica                                                                    |

|----------------------|----------------|--------------------|----------|----------------------------------------------------------------------------------------|

| CALL etiqueta lejana | 9A 00 10 D3 09 | CALL FAR PTR MEMF  | Código   | SP← SP -2;<br>[SP+1:SP]← CS;<br>CS←09D3H;<br>SP← SP -2;<br>[SP+1:SP]← IP;<br>IP← 1000H |

|                      | FF 1E 00 10    | CALL [MEMWWDS]     | Datos    | Similar al anterior excepto:<br>CS ←[1003H:1002H];<br>IP ← [1001H:1000H]               |

|                      | FF 1D          | CALL DWORD PTR[DI] | Datos    | Similar al anterior excepto:<br>CS←[DI+3:DI+2];<br>IP←[DI+1:DI]                        |

#### Instrucciones de Retorno de Subrutina.

| Mnemónico                    | Código   | Mnemónico | Segmento | Operación simbólica                                             |

|------------------------------|----------|-----------|----------|-----------------------------------------------------------------|

| RET n (cercano) <sup>f</sup> | C3       | RET       | Pila     | IP ← [SP+1:SP];<br>SP← SP +2;                                   |

|                              | C2 08 00 | RET 8     | Pila     | IP←[SP+1:SP];<br>SP← SP + 2 + 8                                 |

| RET n (lejano) <sup>f</sup>  | СВ       | RET       | Pila     | IP←[SP+1:SP];<br>SP← SP + 2;<br>CS ←[SP+1:SP];<br>SP←SP+2       |

|                              | CA 08 00 | RET 8     | Pila     | IP ← [SP+1:SP];<br>SP←SP + 2;<br>CS←[SP+1:SP];<br>SP←SP + 2 + 8 |

### Tema 2. Características del Microprocesador 80X86. Instrucciones de Push y Pop.

| Mnemónico general | Código Objeto | Mnemónico  | Segmento    | Operación simbólica                    |

|-------------------|---------------|------------|-------------|----------------------------------------|

| PUSH fuente       | 51            | PUSH CX    | Pila        | SP←SP-2;<br>[SP+1]←CH; [SP]←CL         |

|                   | 1E            | PUSH DS    | Pila        | SP←SP-2;<br>[SP+1:SP]←DS               |

|                   | FF 75 02      | PUSH[DI+2] | Pila, datos | SP←SP-2;<br>[SP+1]←[DI+3]; [SP]←[DI+2] |

| POP dest          | 59            | POP CX     | Pila        | CL←[SP]; CH←[SP+1];<br>SP←SP+2         |

|                   | 1F            | POP DS     | Pila        | DS←[SP+1:SP];<br>SP←SP+2               |

|                   | 8F 45 02      | POP[DI+2]  | Datos, pila | [DI+3]←[SP+1]; [DI+2]←[SP];<br>SP←SP+2 |

| PUSHF             | 9C            | PUSHF      | Pila        | SP←SP-2;<br>[SP+1:SP]← Banderas        |

| POPF              | 9D            | POPF       | Pila        | Banderas←[SP+1:SP];<br>SP←SP+2         |

### Tema 2. Características del Microprocesador 80X86. Instrucciones de Interrupciones.

| Mnemónico general | Código Objeto | Mnemónico | Segmento de memoria                                                   | Operación simbólica                                                                                                                                                                |

|-------------------|---------------|-----------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT tipo          | CD 23         | INT 23H   | Pila e interrupción saltando a la tabla de vectores ( 00000 a 003FFH) | SP← SP -2;<br>[SP+1:SP]← Banderas<br>IF←0; TF←0;<br>SP← SP -2;<br>[SP+1:SP]← CS;<br>CS←[0008FH:0008EH];<br>SP← SP -2;<br>[SP+1:SP]← IP;<br>IP←[0008DH:0008CH]                      |

| INTO              | CE            | INTO      | Pila e interrupción saltando a la tabla de vectores (00000 a 003FFH)  | Si OF=1, entonces<br>SP← SP -2<br>[SP+1:SP]← Banderas;<br>IF=0; TF=0;<br>SP← SP -2;<br>[SP+1:SP]← CS;<br>CS←[00013H:00012H];<br>SP← SP -2;<br>[SP+1:SP]←IP;<br>IP ←[00011H:00010H] |

| IRET              | CF            | IRET      | Pila                                                                  | $IP \leftarrow [SP+1:SP];$ $SP \leftarrow SP + 2;$ $CS \leftarrow [SP+1:SP];$ $SP \leftarrow SP + 2;$ $Banderas \leftarrow [SP+1:SP];$ $SP \leftarrow SP + 2$                      |

#### Instrucciones de Control del Procesador.

| Mnemónico general  | Código<br>objeto | Mnemónico          | Segmento de<br>memoria | Operación simbólica           |

|--------------------|------------------|--------------------|------------------------|-------------------------------|

| STC                | F9               | STC                | Dentro del CPU         | CF <b>←</b> 1                 |

| CLC                | F8               | CLC                | Dentro del CPU         | CF ← 0                        |

| CMC                | F5               | CMC                | Dentro del CPU         | $CF \leftarrow \overline{CF}$ |

| STD                | FD               | STD                | Dentro del CPU         | DF <b>←</b> 1                 |

| CLD                | FC               | CLD                | Dentro del CPU         | DF ← 0                        |

| STI                | FB               | STI                | Dentro del CPU         | IF <b>←</b> 1                 |

| CLI                | FA               | CLI                | Dentro del CPU         | IF ← 0                        |

| HLT                | F4               | HLT                | Dentro del CPU         | Ninguna                       |

| WAIT               | 9B               | WAIT               | Dentro del CPU         | Ninguna                       |

| LOCK Instrucción   | F0 A1 00 10      | LOCK MOV AX,MEMWDS | Datos                  | Ninguna                       |

| NOP                | 90               | NOP                | Dentro del CPU         | Ninguna                       |

| ESC número, fuente | DE 0E 00 10      | ESC 31H,MEMWDS     | Datos                  | Bus de datos ←[MEMWDS]        |

#### Instrucciones de Control del Procesador.

| Mnemónico general  |                    | Segmento de memoria    | Operación                                                                                                                                                                                                                                                                                                            |

|--------------------|--------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT               | WAIT               | Ninguna                | Pone en estado de espera (TEST=1) al procesador hasta que el coprocesador termina su ejecución.                                                                                                                                                                                                                      |

| LOCK Instrucción   | LOCK MOV AX,MEMWDS | Ninguna                | Bloquea el bus. Evita que el 8087 u otros coprocesadores cambien datos al mismo tiempo que el procesador; coloca la línea de salida $\overline{LOCK} = 0$ . Lock es un prefijo de un byte que se utiliza para prevenir a los coprocesadores de acceder al bus hasta que Se complete la instrucción siguiente a lock. |

| NOP                | NOP                | Ninguna                | No operación.                                                                                                                                                                                                                                                                                                        |

| ESC número, fuente | ESC 31H,MEMWDS     | Bus de datos ←[MEMWDS] | Coloca el contenido del operando fuente de memoria en el bus de datos y ejecuta un NOP. El primer operando identifica una instrucción escape particular para que sea Ejecuta por el coprocesador.                                                                                                                    |

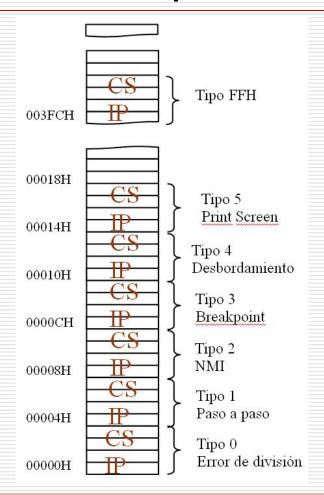

### Interrupciones Tabla de Vectores de Interrupción

- □ La Tabla de vectores de interrupción se ubica en los primeros 1024 bytes de memoria (00000H- 003FFH) contiene 256 vectores de interrupción diferentes de 4 bytes.

- ☐ Un vector de interrupción contiene la dirección (segmento de código y desplazamiento IP) del procedimiento de interrupción.

- Los dos bytes menos significativos contienen el IP y los dos bytes más significativos contienen el CS.