# Sistemas Digitales con Microprocesadores 112135

# Tema 4. Temporización del Bus.

# Sistemas Digitales con Microprocesadores 112135

#### Tema 4. Temporización del Bus.

- 1. Retención del bus de Direcciones

- 1.1 Demultiplexación de los buses

- 1.2 El sistema de retención

- 1.3 Temporización del Bus. Ciclo de Lectura y Ciclo de Escritura.

- 1.4 Generador de reloj 8284.

- 1.5 El controlador de bus 8288

#### **TERMINALES DEL 8086**

#### SEÑALES COMUNES A LOS DOS MODOS DEL 8086

- AD<sub>0</sub> a AD<sub>15</sub>: bus de direcciones/datos multiplexados

- $A_{16}/S_3$ ,  $A_{17}/S_4$ ,  $A_{18}/S_5$  y  $A_{19}/S_6$ : en estas cuatro salidas multiplexadas el  $\mu P$  libera los

- cuatro bits más significativos de direcciones y después las señales de estado.

- BHE'/S<sub>7</sub>: en esta salida multiplexada el μP libera la señal BHE' validando el byte más

- significativo del bus de datos y luego una señal de estado.

- RD': señal de lectura

- **READY**: sincronización con las memorias o los periféricos lentos.

- CLK: entrada de reloj del 8086

- RESET: inicialización del 8086

- NMI : solicitud de interrupción no enmascarable se activa en flanco ascendente

- INTR : solicitud de interrupción enmascarable activada en el nivel alto

- TEST' sincronización con un procesador especializado

|      |                 | Modo<br>Máximo | Modo<br>Mínimo |

|------|-----------------|----------------|----------------|

| GND  | $\sqsubseteq_1$ | 40 ⊨VCC        |                |

| AD14 | <b>⊨</b> 2      | 39 ⊨AD15       |                |

| AD13 | <b>⊣</b> 3      | 38 ⊨A16/S3     |                |

| AD12 | <b>⊣</b> 4      | 37 ⊨A17/S4     |                |

| AD11 | <b>⊣</b> 5      | 36 ⊨A18/S5     |                |

| AD10 | <b>⊣</b> 6      | 35 ⊨A19/S6     |                |

| AD9  | 7               | 34 ⊨BHE'/S7    |                |

| AD8  | 8               | 33 ⊨MN/MX' ¦   |                |

| AD7  | 9               | 32   RD'       |                |

| AD6  | 10              | 31   RQ'/GT0'; | HOLD           |

| AD5  | 11              | 30   RQ'/GT1'; | HLDA           |

| AD4  | 12              | 29 HLOCK'      | WR'            |

| AD3  | 13              | 28   S2'       | M/IO'          |

| AD2  | 14              | 27 ⊨S1'        | DT/R'          |

| AD1  | 15              | 26 片S0'        | DEN'           |

| AD0  | 16              | 25 ⊨QS0        | ALE            |

| NMI  | 17              | 24   QS1       | INTA'          |

| INTR | 18              | 23   TEST'     |                |

| CLK  | 19              | 22   READY     |                |

| GND  | └── 20          | _21 ⊢RESET     |                |

Configuración de terminales del 8086

## **TERMINALES DEL 8086**

| • M/IO': selección de una localidad de memoria (M/IO'=1) o de un periférico (M/IO'=0) • WR': señal de escritura                                                                                                                                                                                                                        | SEÑALES ESPECIFICAS AL MODO MAXIMO  Solve | GND 1<br>AD14 2<br>AD13 3<br>AD12 4<br>AD11 5 | Modo<br>Máximo<br>40 VCC<br>39 AD15<br>38 A16/S3<br>37 A17/S4<br>36 A18/S5                                                                                                                                   | Modo<br>Mínimo                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| <ul> <li>INTA': reconocimiento de interrupción</li> <li>DT/R': Señales necesarias para</li> <li>DEN': el control de los circuitos buffers del bus de datos</li> <li>ALE: señal de validación de la dirección</li> <li>HOLD: solicitud de acceso directo a memoria</li> <li>HLDA: reconocimiento de acceso directo a memoria</li> </ul> | <ul> <li>RQ'/GT0', RQ'/GT1': solicitudes y autorizaciones de acceso al bus.</li> <li>LOCK': prohibición de acceso al bus en funcionamiento multiprocesador</li> <li>QS<sub>0</sub>, QS<sub>1</sub>: estado de la cola de espera</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | AD10                                          | 35   A19/S6<br>34   BHE'/S7<br>33   MN/MX'<br>32   RD'<br>31   RQ'/GT0'<br>30   RQ'/GT1'<br>29   LOCK'<br>28   S2'<br>27   S1'<br>26   S0'<br>25   QS0<br>24   QS1<br>23   TEST'<br>22   READY<br>21   RESET | HLDA<br>WR'<br>M/IO'<br>DT/R'<br>DEN'<br>ALE<br>INTA' |

#### **TERMINALES DEL 8086**

| $\overline{\overline{S}}_2$ | $\overline{\overline{S}}_1$ | $\overline{S}_0$ | Tipo de transferencia en curso |

|-----------------------------|-----------------------------|------------------|--------------------------------|

| 0                           | 0                           | 0                | Reconocimiento de interrupción |

| 0                           | 0                           | 1                | Lectura de periférico          |

| 0                           | 1                           | 0                | Escritura de periférico        |

| 0                           | 1                           | 1                | Halt                           |

| 1                           | 0                           | 0                | Búsqueda de una instrucción    |

| 1                           | 0                           | 1                | Lectura de memoria             |

| 1                           | 1                           | 0                | Escritura de memoria           |

| 1                           | 1                           | 1                | Nada                           |

| S <sub>4</sub> | S <sub>3</sub> | Segmento<br>seleccionado |

|----------------|----------------|--------------------------|

| 0              | 0              | Extra                    |

| 0              | 1              | Pila                     |

| 1              | 0              | Código                   |

| 1              | 1              | Datos                    |

|                |                |                          |

|                |                |                          |

|                |                |                          |

|                |                |                          |

| QS1 | QSO | Estado de la                                                                |  |

|-----|-----|-----------------------------------------------------------------------------|--|

|     | 230 | cola de espera                                                              |  |

| 0   | 0   | Ninguna operación en curso                                                  |  |

| 0   | 1   | El primer byte de una instrucción se ha                                     |  |

| 1   | 0   | extraído de la cola de espera<br>La cola de espera se ha reinicializado     |  |

| 1   | 1   | El siguiente byte de una instrucción se<br>ha extraído de la cola de espera |  |

- S5 es una copia del bit de bandera de "interrupción" I

- S6 está en nivel cero.

- S7 es un bit de estado inutilizado disponible para una eventual versión del 8086

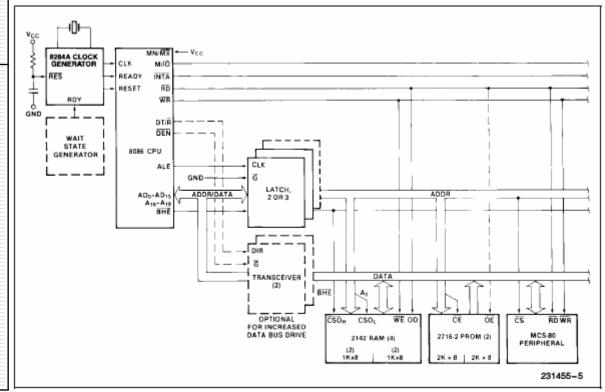

## Configuración en Modo mínimo 8086

#### SEÑALES ESPECIFICAS AL MODO MINIMO

• M/IO': selección de una localidad de memoria (M/IO'=1)

o de un periférico (M/IO'=0)

• WR': señal de escritura

• INTA': reconocimiento de interrupción

• DT/R': Señales necesarias para

• **DEN**': \( \right\) el control de los circuitos \( \right\) buffers del bus de datos

• ALE : señal de validación de la dirección

• HOLD: solicitud de acceso directo a memoria

• HLDA: reconocimiento de acceso directo a memoria

Figure 4a, Minimum Mode 8086 Typical Configuration

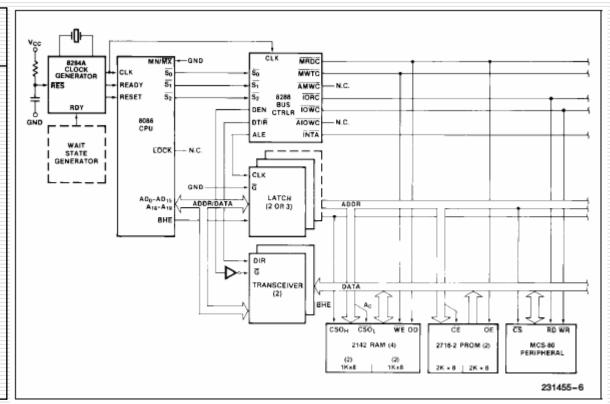

## Configuración en Modo máximo 8086

#### SEÑALES ESPECIFICAS AL MODO MAXIMO

- S<sub>0</sub>, S<sub>1</sub>, S2 : señales de estado decodificadas por el 8288

- RQ'/GT0', RQ'/GT1': solicitudes y autorizaciones de acceso al bus.

- LOCK': prohibición de acceso al bus en funcionamiento multiprocesador

- QS<sub>0</sub>, QS<sub>1</sub>: estado de la cola de espera

Maximum Mode 8086 Typical Configuration

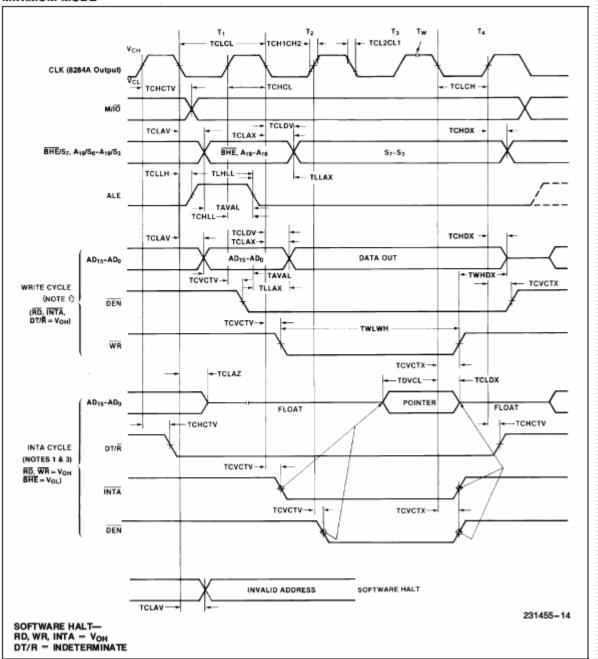

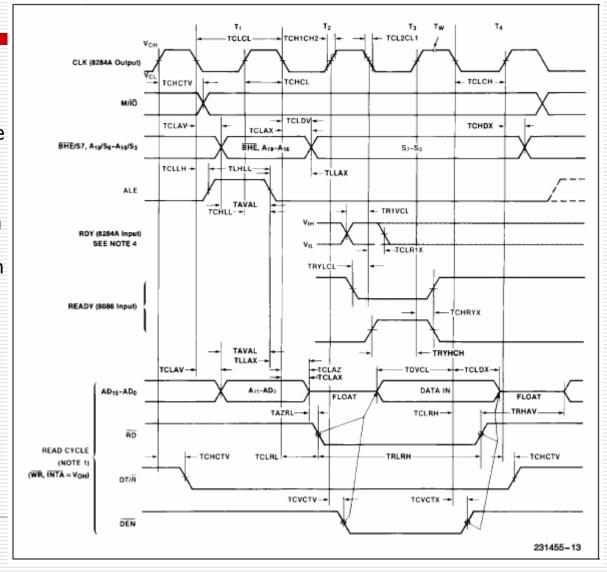

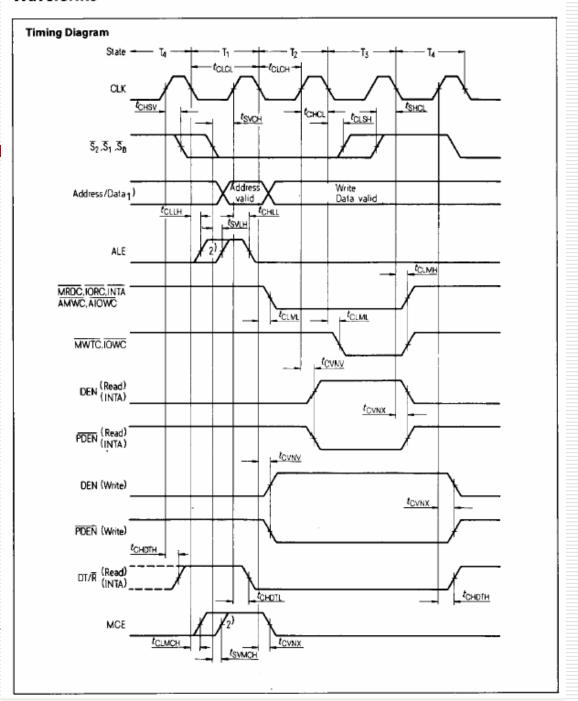

□ El 8086 es un microprocesador de 16 bits con una capacidad de direccionamiento de memoria de 1 MB (2<sup>20</sup>) y un espacio de puertos de E/S con una capacidad de 64 KB (2<sup>16</sup>). El CPU se comunica con su ambiente externo a través del bus multiplexado de direcciones, datos y status y un bus de control. Para transferir datos o buscar instrucciones, el CPU ejecuta un ciclo de bus. El ciclo de bus mínimo consiste de cuatro ciclos de reloj del CPU llamados estados T.

Durante el primer estado T (T1), el CPU coloca una dirección en los 20 bits del bus multiplexado de direcciones/datos/status. Durante T2, las cuatro líneas más significativas del bus se cambian de direcciones (A19-A16) a señales de estado (S6, S5, S4, S3). La información de estado es principalmente para monitoreo de diagnóstico.

#### MINIMUM MODE

8086

Durante el segundo estado T (T2), el CPU remueve la dirección del bus y coloca en tercer estado sus 16 líneas de salida menos significativas del bus en preparación de un Ciclo de lectura o coloca los datos en esas 16 líneas en un ciclo de escritura. Los buffers bidireccionales se habilitan en el tiempo T1 o T2 dependiendo de la dirección de la transferencia (hacia adentro o hacia fuera del CPU). Los comando de lectura, escritura o reconocimiento de interrupción se habilitan siempre en T2.

#### MINIMUM MODE

- El CPU continua proporcionando la información de estado en las cuatro líneas más significativas del bus durante T3 y continuará con los datos de escritura o muestreando los datos de lectura en las 16 líneas menos significativas del bus. Si la memoria seleccionada o el dispositivo de E/S no es capaz de transferir los datos a la máxima velocidad de transferencia del CPU, el dispositivo debe señalizar al CPU indicando que no está listo y forzar al CPU a insertar tiempos de espera TW después de T3. La indicación de "no listo" debe presentarse al CPU al inicio de T3.

- La actividad del bus durante TW es la misma que la de T3. Cuando el dispositivo seleccionado ha tenido suficiente tiempo para completar la transferencia, este coloca la seña "READY" (listo) y permite al CPU continuar. El CPU retendrá el dato en el bus durante el último estado de espera o durante T3 si no existió solicitud de estados de espera. El ciclo de bus termina en T4, las líneas de comando se deshabilitan y los dispositivos externos seleccionados son deshabilitados del bus.

- El ciclo de bus aparece para los dispositivos en el sistema como un evento asíncrono que consiste de una dirección que selecciona al dispositivo seguido de un habilitador de lectura o datos y una habilitación de escritura. El dispositivo seleccionado acepta los datos del bus durante un ciclo de escritura y coloca el dato solicitado en el bus durante un ciclo de lectura. A la terminación del comando, el dispositivo retiene el dato de escritura o deshabilita sus manejadores de salida del bus. El único control que el dispositivo tiene en el bus es la inserción de ciclos de espera.

- El 8086 solo ejecuta un ciclo de bus cuando las instrucciones u operandos deben ser transferidos hacia o desde la memoria o dispositivos de E/S. Cuando no se ejecuta un ciclo de bus, la interfaz de bus ejecuta ciclos ociosos (TI, idle cycle). Durante los estados ociosos, el CPU continúa con la información de status del ciclo previo en las líneas de dirección más significativas. Si el ciclo previo fue de escritura, el CPU continúa manejando los datos de escritura en el bus multiplexado hasta que inicie el siguiente ciclo de bus, Si el CPU ejecutas ciclos TI seguidos de un ciclo de lectura, el CPU no manejará las 16 líneas menos significativas del bus hasta que se requiera el siguiente ciclo de bus.

#### Conceptos del Bus de Direcciones Retención del Bus de Direcciones

Debido a que la mayoría de memorias y periféricos requieren una dirección estable durante todo el ciclo de bus, la dirección del bus multiplexado de direcciones/datos durante T1 debe ser retenida y esta dirección retenida se utilizará para seleccionar la localidad de memoria o periférico deseada a través de una decodificación.

#### Conceptos del Bus de Direcciones

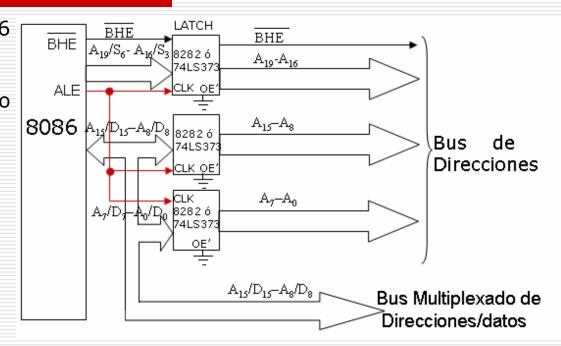

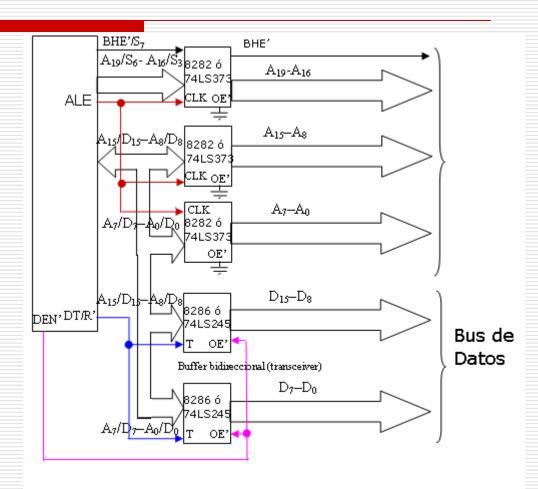

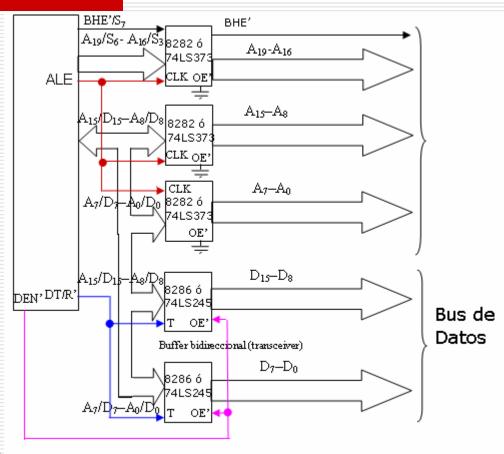

Para demultiplexar el bus el 8086 proporciona la señal ALE (address latch enable) para capturar la dirección en el 8282 o en 74LS373 (8-bit biestable latch). Estos latches tienen salidas con buffers de tercer estado que proporcionan una capacidad de 32 mA y pueden conmutar una carga capacitiva de 300 pF en 22 ns. Estos circuitos propagan la dirección a través de las salidas mientras ALE está en nivel alto y retienen la dirección en la bajada de ALE. Las salidas se habilitan a través de entrada OE'.

- Para el sistema de bus de datos, se pueden considerar dos alternativas: el **bus multiplexado de direcciones/datos** y el **bus de datos con buffers** utilizando transceivers (buffers bidireccionales).

- Si una memoria o un dispositivo de E/S se conecta directamente al bus multiplexado, el diseñador debe garantizar que los dispositivos no corrompan la dirección en el bus durante T1. Para evitar esto, los manejadores de salida de los dispositivos no deben ser habilitados por el selector del circuito (chip select), deben tener un habilitador de salida controlado por la señal de lectura (read) del sistema. La temporización del 8086 garantiza que la señal "read" (activada en T2) no será válida hasta después de que la dirección es retenida por ALE.

bus de datos con buffers

- Se tienen algunas técnicas disponibles para interfazar al bus multiplexado dispositivos que no tienen la terminal de habilitación de salida "output enable". Una opción es conectar el selector del circuito (chip select) con compuertas AND a la señal de RD' y WR' del CPU.

- Una limitación al utilizar el bus multiplexado, es que el 8086 maneja una capacidad de 2.0 mA y una carga capacitiva de 100 pF para garantizar las características especificadas. Asumiendo una carga capacitiva de 20 pF por dispositivo de E/S, 12 pF por latch de direcciones y de 5 a 12 pF por dispositivo de memoria, un sistema constituido por tres periféricos y dos o cuatro dispositivos de memoria está cerca de llegar al límite de carga.

Para satisfacer la carga capacitiva y manejar los requerimientos de sistemas grandes el bus de datos debe tener buffers. Los 8286 ó 74LS245 son transceivers octales no invertidos, tienen buffers de salida de tres estados que manejan 32 mA en la interfase del bus y 10 mA en la interfase del CPU y pueden conmutar cargas capacitivas de 300 pF en la interfase del bus y 100pF en la interfase del CPU en 22 ns. Para habilitar y controlar la dirección de los transceivers, el 8086 proporciona las señales DEN' (Data Enable) y DT/R' (Data transmit/receive). Estas señales proporcionan el tiempo adecuado para garantizar el aislamiento del bus multiplexado del sistema durante T1 y la eliminación de la contención del bus con el CPU durante la lectura y escritura.

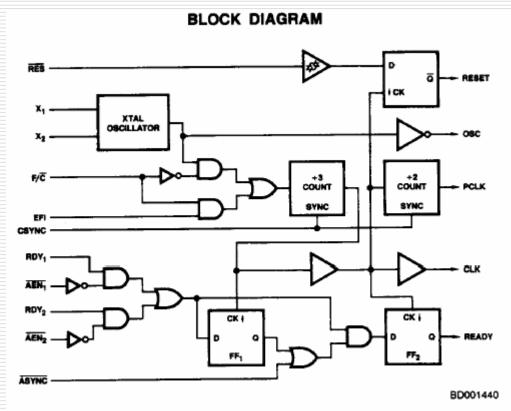

☐ El generador 8284A produce las siguientes funciones o señales básicas:generación de reloj, sincronización de reinicialización, sincronización de la señal lista (ready) y señal periférica de reloj de nivel TTL.

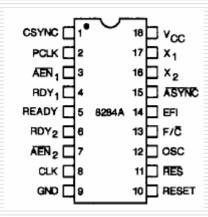

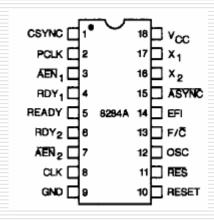

## Generador de Reloj 8284 Terminales

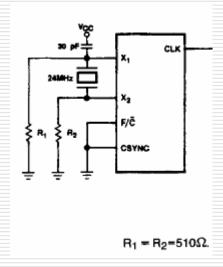

- X1 y X2 son las entradas del cristal, el cual no tiene polaridad. La frecuencia se divide entre 3, con la característica que es de 33% en alto y 66% en bajo, la cual se obtiene en la salida CLK.

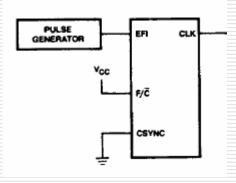

- La señal **CLK** de salida es la que se proporciona al procesador 8086 y otros componentes del sistema. Es un tercio de la frecuencia del cristal o de EFI y tiene un cilo de trabajo del 33%.

- PCLK (reloj periférico) Señal que es un sexto de la frecuencia del cristal o de entrada EFI y tiene un ciclo de trabajo del 50%.

- ☐ **EFI** (external frecuency in) es la entrada de reloj si se usa oscilador u otra señal de frecuencia externa.

- La terminal F/C ´ determina cuál es la señal de origen, si ésta está en 1,el origen es la señal EFI, si no, será la obtenida en X1 y X2 (cristal).

- OSC es una señal de salida donde se obtiene la frecuencia del cristal en una sola terminal.

- RES´ es una línea de entrada para el disparo de la señal de RESET. Aquí se conecta un arreglo de capacitorresistencia con un botón de disparo normalmente abierto (push button).

- □ RESET es la señal de inicialización que se envía al microprocesador.

- READY se conecta directamente a la señal READY del 8086.

- AEN1´y AEN2´ se utilizan para solicitar tiempos de espera junto con las entradas RDY1 y RDY2.Los estados de espera se generan en la terminal READY.

- ASYNC´ se emplea para seleccionar una o dos estapas de de sincronización para las terminales RDY 1 y RDY2.

- CSYNC Sincronización de reloj, se emplea siempre q ue la entrada EFI proporcione la temporización en sistemas multiprocesadores. En el modo mínimo se conecta a GND.

☐ Generador de reloj

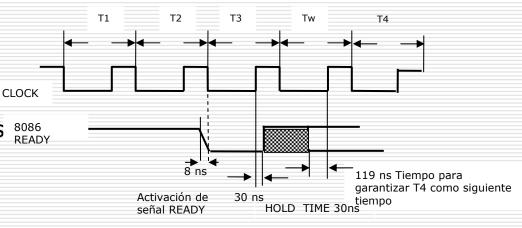

- Los tiempos de espera son tiempos adicionales a T3 en los cuales el 8086 retiene los datos, direcciones y señales de control en una condición estática. Los estados de espera se solicitan habilitando la entrada READY del 8086 en 0 antes de la bajada del reloj en T3. READY debe estar retenido en "0" hasta al menos 30 ns después de que el reloj regrese a 1.

- □ Para evitar un estado de espera adicional READY debe regresar a "1" 119 ns antes de la subida del reloj en Tw.

Sistema insertando un tiempo de espera

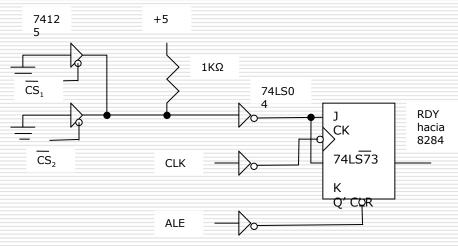

### Circuito para un tiempo de espera

La mayoría de las memorias y dispositivos de E/S los cuales no pueden operar a la máxima frecuencia del CPU típicamente no requieren más de un estado de espera.

La línea de Listo del sistema es manejada a "0" siempre que un dispositivo requiera de un estado de espera. El flip flop es puesto a cero a través de ALE, colocando RDY de 8284 en "1", Si ningún estado de espera es requerido, el flip flop no cambia. Si el sistema requiere de tiempos de espera, (algún CS' de una memoria o dispositivo lento se activa), el flip flop cambia en la transición de cero a uno de T2 para forzar un estado de espera. En la siguiente transición de reloj de cero a uno cambia de nuevo el flip flop para indicar que se encuentra listo y permite completar el ciclo de bus. Cambios posteriores en el flip flop, no afectarán el ciclo de bus.

Figura. Generador de un Estado de Espera

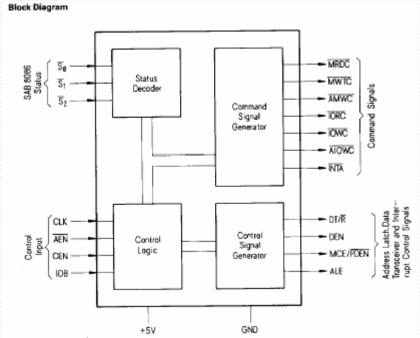

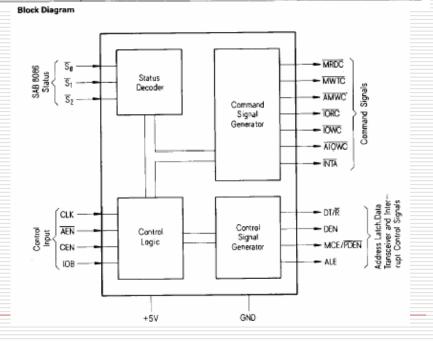

☐ Un sistema 8086 que funcione en modo máximo debe tener un controlador de bus 8288 para generar las señales de modo mínimo que se eliminan durante el funcionamiento en modo máximo

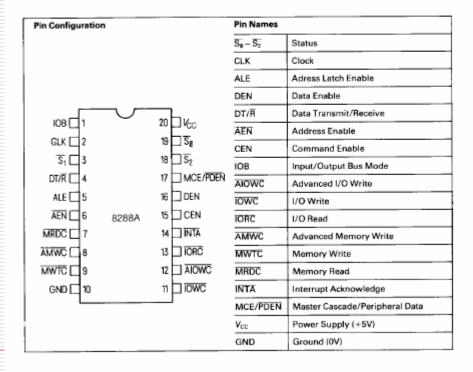

# 8288A Bus Controller for SAB 8086 Family Processors

- Fully compatible with SAB 8288

- 40% Less Power Supply Current than Standard SAB 8288

- Bipolar Drive Capability

- Provides Advanced Commands

- Provides Wide Flexibility in System Configurations

- 3-State Command Output Drivers

- Configurable for Use with an I/O Bus

- Facilitates Interface to One or Two Multi-Master Busses

- □ S2', S1' y S0': Entradas de estado que se decodifican para generar las señales de sincronización para el sistema.

- CLK: Entrada que produce la temporización interna se conecta a la salida CLK del 8284A.

- ALE:Habilitación de dirección para demultiplexar el bus de direcciones.

- DEN: Habilitación de los buffers bidireccionales. La polaridad es inversa a la del procesador.

- DT/R': Transmitir/recibir datos controla el sentido de los buffers bidireccionales.

- □ AEN': Habilitación de dirección, entrada al 8288 que habilita las señales de control de la memoria.

| S2 | \$1 | Śö  | Processor State       | SAB 8288A Command |

|----|-----|-----|-----------------------|-------------------|

| 0  | 0   | 0   | Interrupt Acknowledge | INTA              |

| 0  | 0   | 1   | Read I/O Port         | IORC              |

| 0  | 1   | . 0 | Write I/O Port        | IOWC, AJOWC       |

| С  | 1   | 1   | Halt                  | None              |

| 1  | 0   | 0   | Code Access           | MRDC              |

| 1  | 0   | 1   | Read Memory           | MRDC              |

| 1  | 1   | 0   | Write Memory          | MWTC, AMWC        |

| 1  | 1   | 1   | Passive               | None              |

- CEN: Habilitar control. Estrada que habilita las señales de comando de salida del 8288.

- ☐ IOB: Modo de Bus de E/S: Selecciona el funcionamiento en modo bus de E/S o en el modo bus del Sistema.

- □ AIOWC': Comando Avanzado de escritura de E/S

- IOWC': Comando de escritura de E/S

- □ IORC': Comando de lectura de E/S

- AMWC': Comando Avanzado de escritura de Memoria

- MWTC': Comando de escritura de Memoria

- MRDC': Comando del lectura de Memoria

- □ INTA': Reconocimiento de Interrupción

- MCE/PDEN': Cascada principal/datos periféricos

| S2 | 51 | Śö  | Processor State       | SAB 8288A Command |

|----|----|-----|-----------------------|-------------------|

| 0  | 0  | 0   | Interrupt Acknowledge | INTA              |

| 0  | 0  | 1   | Read I/O Port         | IORC              |

| 0  | 1  | . 0 | Write I/O Port        | IOWC, AIOWC       |

| С  | 1  | 1   | Halt                  | None              |

| 1  | 0  | 0   | Code Access           | MRDC              |

| 1  | 0  | 1   | Read Memory           | MRDC              |

| 1  | 1  | 0   | Write Memory          | MWTC, AMWC        |

| 1  | 1  | 1   | Passive               | None              |

Modo bus de E/S: Cuando CEN (command enable) e IOB se activan (en 1 lógico), el 8288 opera en modo bus de E/S. La salida MCE/PDÉN' actúa como una señal de habilitación de periférico. Su función es idéntica a DEN, excepto que ésta únicamente se activa durante instrucciones de E/S. Esto le permite al 8288 controlar dos conjuntos de buses: bus normal del sistema (posiblemente compartido con otros procesadores) y bus de entrada/salida especial para periféricos.

#### **Functional Description**

The command logic decodes the three SAB 80186, SAB 80188, SAB 8086 or SAB 8088 CPU status lines (S<sub>0</sub>, S<sub>1</sub>, S<sub>2</sub>) to determine what command is to be issued. This chart shows the meaning of each status "word".

| S2 | \$1 | Śö  | Processor State       | SAB 8288A Command |

|----|-----|-----|-----------------------|-------------------|

| 0  | 0   | 0   | Interrupt Acknowledge | INTA              |

| 0  | 0   | 1   | Read I/O Port         | IORC              |

| 0  | 1   | . 0 | Write I/O Port        | IOWC, AIOWC       |

| 0  | 1   | 1   | Halt                  | None              |

| 1  | 0   | 0   | Code Access           | MRDC              |

| 1  | 0   | 1   | Read Memory           | MRDC              |

| 1  | 1   | 0   | Write Memory          | MWTC, AMWC        |

| 1  | 1   | 1   | Passive               | None              |

|    |     |     |                       |                   |

The command is issued in one of two ways dependent on the mode of the SAB 8288A Bus Controller.

I/O Bus Mode — The SAB 8288A is in the I/O Bus mode if the IO8 pin is strapped HIGH. In the I/O Bus mode all I/O command lines (IORC, IOWC, AIOWC, INTA) are always enabled (i.e., not dependent on AEN). When an I/O command is initiated by the processor, the SAB 8288A immediately activates the command lines using PDEN and DT/R to control the I/O bus transceiver. The I/O command lines should not be used to control the system bus in this configuration because no arbitration is present. This mode allows one SAB 8288A Bus Controller to handle two external busses. No waiting is involved

when the CPU wants to gain access to the I/O bus. Normal memory access requires a "Bus Ready" signal (AEN LOW) before it will proceed. It is advantageous to use the IOB mode if I/O or peripherals dedicated to one processor exist in a multi-processor system.

System Bus Mode – The SAB 8288A is in the System Bus mode if the IOB pin is strapped LOW. In this mode no command is issued until 115 ns after the AEN Line is activated (LOW). This mode assumes bus arbitration logic will inform the bus controller (on the AEN line) when the bus is free for use. Both memory and I/O commands wait for bus arbitration. This mode is used when only one bus exists. Here, both I/O and memory are shared by more than one processor.

#### 8288

Modo Bus del Sistema Las señales de control están activas sólo si las entradas AEN' e IOB son activo bajo. Esta forma permite que varios 8288 (y 8086) se puedan interfazar al mismo bus. Un árbitro de bus seleccionará al procesador activo habilitando únicamente un 8288 mediante la entrada AEN'). En este modo MCE/PDEN' funciona como MCE (master cascada enable)

#### Waveforms

| CEN | IOB | AEN' | Descripción                                                                                                                      |

|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1   | X    | Modo bus entrada/salida; todas las líneas de control son habilitadas; MC'/PDEN=PDEN.                                             |

| 1   | 0   | 1    | Modo bus del sistema; todas las señales de control son deshabilitadas, el bus está ocupado, esto es controlado por otro maestro. |

| 1   | 0   | 0    | Modo bus del sistema; todas las señales de control son activadas; el bus es libre para usarse; MCE'/PDEN=MCE.                    |

| 0   | X   | X    | Todas las salidas de comando y las salidas de DEN y PDEN' son deshabilitadas.                                                    |

#### Cuestionario

- ☐ ¿Cuáles son los distintos ciclos de bus que tenemos?

- Para cada periodo T de un ciclo de bus de lectura de memoria indique las señales que se activan en cada tiempo.

- Para cada periodo T de un ciclo de bus de escritura de puerto indique las señales que se activan.

- ☐ ¿Cuáles son las funciones que realiza el circuito 8284A?